Alveo U55C数据中心加速卡 安装至服务器并配置环境

板卡的侧面有JTAG接口:

侧面有标准8P的供电接口,我用万用表点过试了一下:

确认无误后安装至服务器:

此时已经可以正确识别到加速卡:

根据官方XRT要求,我们的操作系统环境需要为:

这里我选择Ubuntu22.04.使用BMC进行远程安装:

然后下载安装Vivado,这里过程省略。

使用USB线连接到板卡,也能发现未烧录的板卡:

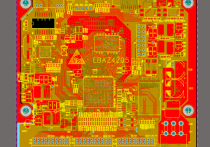

这里提供黄金工程文件的备份( au55c_boardfiles_v1_0_20211104.zip),烧录的时候器件选择

au55c_boardfiles_v1_0_20211104.zip),烧录的时候器件选择

mt25qu01g-spi-x1_x2_x4

烧录之后,需要冷重启,即设备和板卡需要断电,后再启动,此时板卡就已经恢复到出厂状态了。