“EBAZ4205原理图和PCB免费分享 基于ZYNQ7010” 的相关文章

SOC 在线修改设备树和FPGA配置文件 并在线配置FPGA

测试过的平台: 1、DE-10 Cyclone V开发板 ...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...

CDC 单脉冲信号处理

代码中的Sys_clk其实是没有用到的,项目文件:cdc_single.zip//------------------------------------------------------// File Name : cdc.v// Autho...

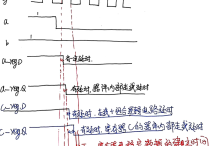

FPGA时序分析和时序约束

时序分析:时序分析的目的就是通过分析FPGA设计中各个寄存器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟之间的关系。一个设计OK的系统,必然能够保证整个系统中所有的寄存器都能够正确的寄存数据。数据和时钟传输路径是由EDA软件,通过针对特定器件布局布线得到的。时序约束:两个作用告知 EDA 软件...

避免Latch产生

Latch简介: Latch其实就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息。 锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,则数据被锁存,输入信号不起作用。因此,锁存器也被称为透...