SOC 在线修改设备树和FPGA配置文件 并在线配置FPGA

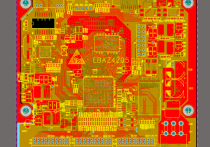

测试过的平台:

1、DE-10 Cyclone V开发板 -> 通过

2、海云捷迅 C5MX系列 Cyclone V开发板 -> 通过

3、小梅哥AC501 Cyclone V开发板 -> 通过

更新FPGA配置程序:点击下载

请连接至开发板并新建一个sh文件,内容如下

#!/bin/sh

if [ -f "soc_system.rbf" ];then

if [ -f "soc_system.dtb" ];then

clear

echo ----------------------------------------------------------------------------------

echo INFO: This program was developed by ChanRa1n and all rights reserved.

umount /soctemp

rm -rf /soctemp

mkdir /soctemp

mount /dev/mmcblk0p1 /soctemp

echo INFO: disk mount success!

cp soc_system.rbf /soctemp/soc_system.rbf

cp soc_system.dtb /soctemp/soc_system.dtb

sleep 3s

echo INFO: soc data copy success!

/soctemp/hps_config_fpga /soctemp/soc_system.rbf

sleep 3s

umount /soctemp

echo INFO: disk umount success!

rm -rf /soctemp

echo INFO: clean temp file success!

echo INFO: soc flash finished!

echo If an error occurs in the process, please restart the development board manually!

echo ----------------------------------------------------------------------------------

else

echo ERROR: soc_system.dtb not exists!

fi

else

echo ERROR: soc_system.rbf not exists!

fi

接下来,请将dtb文件和rbf文件放置和sh文件同一级目录,并运行以下命令:

chmod +x flashsoc.sh && sh ./flashsoc.sh

运行示例:

---------------------------------------------------------------------------------- INFO: This program was developed by ChanRa1n and all rights reserved. INFO: disk mount success! INFO: soc data copy success! INFO: alt_fpga_control_enable(). INFO: alt_fpga_control_enable OK. alt_fpga_control_enable OK next config the fpga INFO: MSEL configured correctly for FPGA image. /soctemp/soc_system.rbf file file open success INFO: FPGA Image binary at 0xb2c64008. INFO: FPGA Image size is 2068700 bytes. ERROR: FPGA failed to program after 5 attempt(s). INFO: alt_fpga_control_disable(). INFO: disk umount success! INFO: clean temp file success! INFO: soc flash finished! If an error occurs in the process, please restart the development board manually! ----------------------------------------------------------------------------------

如果如图所示,出现了ERROR,请重启开发板。(断开开发板电源,并重新上电,或者ssh输入reboot也可以)

如果没有出现ERROR,例如

INFO: alt_fpga_control_enable(). alt_fpga_control_enable OK next config the fpga INFO: MSEL configured correctly for FPGA image, MSELs ==a. C5MB_top.rbf file file open success INFO: FPGA Image binary at 0xb2bd3008. INFO: FPGA Image size is 2058776 bytes. INFO: alt_fpga_configure() successful on the 1 of 5 retry(s). INFO: alt_fpga_control_disable().

则在线配置成功完成!FPGA端的配置已经更新。

如果你只需要对FPGA重新配置,则只需要运行

./hps_config_fpga soc_system.rbf