三模冗余的原理

0.1. 航天相关知识

0.1.1. 三模冗余

0.1.1.1. 原理

三模冗余(TMR)技术是FPGA设计中最著名的错误掩蔽和单事件效应(SEE)保护技术之一。这些FPGA设计大多采用硬件描述语言,如Verilog和VHDL。TMR技术包括设计模块的三倍化和为每个输出端口添加多数表决电路。构建这种三重化方案是一项非常重要的任务,需要花费大量的时间和精力来修改设计代码。本文开发了RASP-TMR工具,该工具具有以可综合的Verilog设计文件为输入,对设计进行解析和三次复制的功能。该工具还生成了一个顶层模块,其中所有三个模块都被实例化,并最终添加了提议的多数投票电路。该工具以其图形用户界面在MATLAB中实现。该工具简单、快速、用户友好。该工具生成可综合设计,便于用户评估和验证基于FPGA的系统的TMR设计。使用Xilinx ISE工具和ISim模拟器创建了一个仿真场景。在模拟过程中,对不同的故障模型进行了检验,如位翻转和卡死在1/0。使用各种基准测试设计的结果表明,该工具生成了可综合的代码,并且所提出的多数投票逻辑完美地掩盖了错误/失败。故障注入;容错;可靠性;单事件效应;三模冗余;Verilog-HDL

对选取的关键存储器进行三模冗余,将判决后结果送出给其他模块使用,同时将判决结果反馈给存储器输入部分进行纠错 。

SEU效应会在星上FPGA器件中引起寄存器、存储器逻辑状态变化,该型号FPGA器件寄存器均经过三模冗余处理,但存储器未进行三模处理,导致核心数据存储器出现bit反转,随着时间的增加错误累计造成功能失效。

对选取的存储器进行三模冗余,将判决后结果送出给其他模块使用,同时判断三个冗余域的结果,一旦有一个冗余域出现错误,利用判决后结果对存储器存储的数据进行更新,对错误进行纠正。

设计中,使用三模冗余的方法来对SRAM型FPGA进行单粒子效应防护时,要对单粒子效应常见发生部位,如配置存储器、BRAM等进行有效的抗单粒子防护措施。

0.1.1.2. 代码实现方法

reg in;

wire a,b,c;

assign a=in;

assign b=in;

assign c=in;

assign out=(a|b)&(b|c)&(a|c);

例如in=0,那么正常情况下a=b=c=in=0,倘若此时有个带电粒子击中了任意一个a或者b或者c,假设击中的是a,令a在瞬间变成了1,b和c维持为1。

那么out输出的值为0,没有发生错误。

0.1.1.3. 软件实现方法

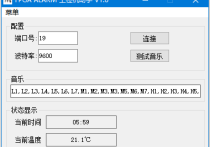

对于Xilinx的基础器件,可以使用TMR Tools,软件使用方法这里略。

DC综合的功能是读取设计的RTL代码并且根据时序约束,综合RTL代码到结构级,从而产生一个映射后的门级网表,其中一个重要的步骤是指定综合所使用的综合库,综合库一般由流片厂商提供,库中包含了引脚到引脚的时序,面积,引脚类型和功耗等信息,综合后的门级网表中的单元也就是库中所定义的单元。

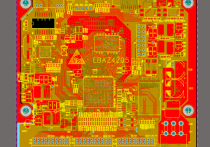

三模冗余的加固过程实际上就是为设计中的每个触发器生成2个冗余触发器并加上表决逻辑,而RTL代码中无法反应出这点,因此可以对原设计综合后的门级网表进行修改,把触发器改为三模冗余触发器,用门级描述编写三模冗余触发器模块,然后和修改的网表一起再次综合就可得到三模冗余加固后的网表文件。值得说明的是DC综合库里面有多种类型的触发器,比如SDFF,EDFF,SEDFF,JK,DFF,即使在综合脚本中限定只用DFF触发器,也会有好几种,所以对于不同的单元要编写相应的三模冗余触发器模块(其结构如图1所示)。此外由于有3路时钟信号,所以要编写时钟生成模块,其功能是由clk产生互有延迟的2路时钟信号。

首先在Synopsys的综合工具DsignCompiler下对原设计的RTL代码进行综合,得到电路的门级网表。门级网表中的电路实际上就是通过例化综合库的单元来描述电路的结构,可以使用形式验证工具Formality来验证RTL代码和综合后的门级网表在功能上是否一致。

然后修改门级网表,在网表中增加线网类型ck[2:0],并且实例化clkgen模块,再把网表里面的触发器改为三模冗余触发器,并修改其时钟端口为{clk,ck[1:0]},由于综合库中不含有这两个模块,这时网表中就出现了两个综合工具没有处理的模块,时钟生成模块和三模冗余触发器模块,修改后的网表就不是完全映射后的门级网表。

最后对修改后的网表,时钟生成模块及三模冗余触发器模块进行再次综合,这次综合实际上就是对时钟生成模块和三模冗余触发器的综合,把它们映射为综合库中的单元,得到的门级网表即是三模冗余加固后设计的门级网表。

由于三模冗余触发器单元的时钟端口有3位,即使在库中加入三模冗余触发器的单元,综合器也无法把设计直接映射成该单元,因此可以把时钟生成模块放到TMR_DFF内部,这样三模冗余触发器时钟端口就只有1位,在库文件中把触发器单元用对应的三模冗余触发器单元替换掉,DC就可以把电路中的触发器直接映射成TMR_DFF,一次综合就可以完成设计了,但是这样一来整个芯片的面积又会增大很多(时钟生成模块不在共用),除此之外也可以借助上面的方法在原设计综合后修改网表。前面已经提到库文件里面有很多种类型的触发器,所以应对不同的DFF触发器建立相应的库单元,下面是一种建立库单元的方法,主要分为2步:版图设计和仿真特性提取。

单元库的建立首先要完成单元的版图设计,在确定单元库所包含的单元种类和单元电路后,根据加工厂家的工艺参数,设计规则等完成单元的版图设计,并导出电路网表,此时网表中不仅有电路结构,还有电阻,电容参数。然后就可以进行单元的参数提取工作。

参数提取需要选择一种用于参数提取的工具,这里选择siliconsmart,其次要确定模拟仿真工具,如HSpice。主要步骤包括创建工作目录配置仿真环境,引入参考库,产生仿真文件,运行仿真特性提取,生成库文件。

创建工作目录是指创建一个用于siliconsmart运行的目录,此时会自动生成一个名为config.tcl的脚本文件,需要手动对其进行一些关键配置,主要包括模拟工具的选择(这里选择HSpice),模拟模型的指定,环境温度等变量的设置等。引入参考库是为工具指定一个参考的库单元,工具将参考单元的信息摘取出来,并为该单元生成一个控制文件,该文件详细描述了需要提取的单元的信息。包括单元网表文件,管脚信息,逻辑功能,输入信号的上升/下降时间,输出管脚负载情况等。如果没有参考的库文件,则需要手动编写该文件。产生仿真文件是告诉工具对单元的哪些方面进行特性提取,比如时序,功耗,CCS模型等。运行仿真提取是对单元进行模拟仿真特性提取工作。生成库文件会产生2个库单元,其中.v是仿真工具用的仿真库,.lib是可读的综合库,可以在DC中用read_lib *.lib命令读入.lib文件,然后用write_ lib* *.db命令可以生成.db综合库(*代表库单元的名字)。

对于抗辐射加固来说,除了用电路加固外可能还需要选择更加可靠的工艺,SOI工艺就具有很好的抗辐射性能,它消除了闩锁效应,有效地降低了单粒子效应,而此时就需要建立自己的单元库了,库中的触发器单元就可以直接建成三模冗余触发器的库单元。

注:相关描述性介绍来自网络。