“(手册)SpyGlass® CDC Customer Training Release 5.1.0” 的相关文章

高速ADC模块开源页面 带Verilog示例程序

暂无...

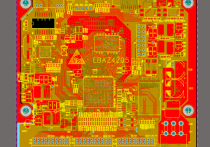

EBAZ4205原理图和PCB免费分享 基于ZYNQ7010

ebit.pdfebit.PcbDoc...

SOC 在线修改设备树和FPGA配置文件 并在线配置FPGA

测试过的平台: 1、DE-10 Cyclone V开发板 ...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

CDC 单脉冲信号处理

代码中的Sys_clk其实是没有用到的,项目文件:cdc_single.zip//------------------------------------------------------// File Name : cdc.v// Autho...

点亮LED灯实验

设计流程:设计规划 -> 波形绘制 -> 代码编写 -> 代码编译 -> 逻辑仿真 -> 波形对比 -> 绑定管脚 -> 分析综合布局布线 -> 上板验证新建项目文件夹(led):Doc:放置文档资料(数据手册、波形图、文档、项目日志)Pri:放置工程...