“已上传pdf,从开发到验证的完整手册《FPGA之道》狄超 刘萌著 西安交通大学出版社 pdf” 的相关文章

ALGO C4MB V11引脚参照表(持续更新)

功能:常用引脚CLKPIN_E1LED0PIN_G15LED1PIN_F16LED2PIN_F15LED3PIN_D16KEY1PIN_E15KEY2PIN_E16KEY3PIN_M15KEY4PIN_M16RXDPIN_M2TXDPIN_G1功能:VGA引脚VGA_BLUE[0]PIN_C15VG...

基础实验十三,DS18B20温度传感器

//==========================================================================// Author : ChanRa1n// Description: Training for Intel FPGA/...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...

全加器(层次化设计)

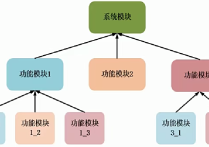

该篇博客根据上一篇半加器的设计,再结合层次化的设计思想来实现一个全加器!层次化设计理论部分:数字电路中根据模块层次的不同有两种基本的结构设计方法:自底向上的设计方法 和 自顶向下的设计方法自底向上(Bottom-Up) 自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存...

时序约束(TCL脚本)

get_ports的使用方法如下:# 获取所有端口 get_ports * # 获取名称中包含data的端口 get_ports *data* # 获取所有输出端口 get_ports -filter {DIRECTION == OUT} # 获取所有输入端口 all...