(公开)载人航天FPGA软件需求分析与研制流程浅析

0.引言

FPGA(现场可编程门阵列)在数字硬件设计领域扮演着重要角色。本篇博文旨在提供一个完整、可操作的指南,详细介绍FPGA软件需求分析与研制流程,并解释其中的关键概念和步骤,帮助读者更好地开展FPGA软件开发工作。本指南将指导您从需求分析到执行与维护的全过程,确保FPGA软件的高质量和可靠性。

1. FPGA研制技术流程

FPGA的研制涉及三类流程:Ⅰ类原型FPGA研制技术流程、Ⅱ类继承FPGA研制技术流程以及Ⅲ类沿用FPGA研制技术流程。每个流程都有关键的质量控制点,即在关键阶段进行正式评审。在任务分析阶段,应进行影响域分析或沿用可行性分析,以确定可能需要更改的部分。

1.1 Ⅰ类原型FPGA研制技术流程

Ⅰ类原型FPGA研制技术流程适用于开发新的FPGA设计。该流程包括需求定义、设计、验证和实施等阶段的迭代和优化过程。在需求定义阶段,团队成员应和项目负责人紧密合作,明确FPGA软件的目标和功能需求。在设计和验证阶段,软件工程师将基于需求定义阶段的结果,进行FPGA软件的架构设计和逻辑设计,然后通过仿真和验证,确保设计的正确性和功能完整性。在实施阶段,将在硬件上实现FPGA设计,涉及物理布线和时序分析,以验证设计在实际硬件上的可行性和准确性。

1.2 Ⅱ类继承FPGA研制技术流程

Ⅱ类继承FPGA研制技术流程适用于基于现有的FPGA设计进行二次开发或优化。这种流程常用于扩展或改进现有的FPGA设计,以满足新的需求。与Ⅰ类原型FPGA研制技术流程相比,Ⅱ类流程可以更快地推进项目,并减少开发成本。在这种流程中,需要充分理解现有的FPGA设计,明确新增功能和改进的目标,并根据这些目标进行验证和实施。

1.3 Ⅲ类沿用FPGA研制技术流程

Ⅲ类沿用FPGA研制技术流程适用于通过使用已经开发和验证的FPGA设计进行再次生产。这种流程常用于大规模生产,其中重点是确保新生成的FPGA软件与之前的版本的一致性和相容性。在这种流程中,需要检查和确认FPGA设计的版本信息,确保使用正确的设计版本,并进行必要的验证和实施。

详细步骤和说明:

在每个流程中,都应包含质量控制点,确保在关键阶段进行正式的评审,以保证FPGA软件的质量和可靠性。

2. FPGA软件需求分析

FPGA软件需求分析是软件开发的核心工作,它确保所开发的FPGA软件能够满足用户的需求。需求分析包括以下步骤和解释:

2.1 需求定义与收集

在需求定义阶段,团队成员应与项目负责人和最终用户紧密合作,明确FPGA软件的目标和功能需求。需求定义的关键活动包括:

定义FPGA软件的功能、性能和界面要求

确定软件的输入和输出数据格式

确定FPGA软件在不同使用情景下的工作条件和环境要求

收集和整理所需的硬件资源和第三方IP核的信息

2.2 需求分析与规格说明书编写

在需求分析阶段,应深入分析和理解需求,将其转化为详细的需求规格说明。关键活动包括:

分析需求的完整性、一致性和可行性

定义FPGA软件的对外接口和内部逻辑结构

制定开发计划和时间安排

编写需求规格说明书,明确软件的功能、性能和质量要求

2.3 需求评审和确认

在需求评审和确认阶段,团队应对需求规格说明书进行评审,并与项目负责人和最终用户达成共识。关键活动包括:

对需求规格说明书进行全面评审,确保规格的准确性、一致性和合理性

与项目负责人和最终用户进行讨论和沟通,解决需求中的疑问和冲突

确认需求规格说明书的最终版本,作为后续开发的基准文档

3. FPGA软件质量保证计划

FPGA软件质量保证计划是确保FPGA软件开发过程中质量控制和质量保证的指导性计划。该计划应包括以下内容的说明和详细解释:

3.1 质量目标和指标

质量目标和指标是FPGA软件质量保证计划的基础,用于评估和监控软件的质量表现。关键活动包括:

设定质量目标,如功能完整性、性能要求和用户体验等

确定可衡量的质量指标,如错误率、响应时间和稳定性等

制定评估和监控质量的方法和工具

3.2 质量控制活动

质量控制活动旨在确保FPGA软件开发过程中质量的一致性和稳定性。关键活动包括:

进行代码审查和静态分析,以识别潜在的错误和漏洞

执行单元测试、集成测试和系统测试,以验证软件的功能和性能

进行性能优化和错误修复,并进行版本管理和配置管理

3.3 问题追踪和缺陷管理

问题追踪和缺陷管理是FPGA软件质量保证计划中必不可少的活动。关键活动包括:

建立问题追踪系统,以跟踪和记录软件开发过程中的问题和缺陷

分类和优先级评估问题,确保及时解决和修复重要的问题

进行持续性改进,以减少和预防类似问题的发生

4. 执行与维护

执行与维护阶段是FPGA软件开发的最后阶段。在这个阶段,FPGA软件被实际执行并进行维护。详细步骤和说明:

4.1 FPGA软件实施

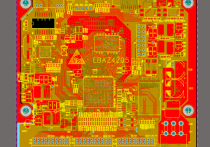

实施阶段是将FPGA软件设计转化为实际硬件的过程。关键活动包括:

进行物理布局和布线,以将FPGA设计映射到实际硬件上

进行时序分析,以确保设计在实际硬件上的时序满足要求

进行时序仿真和验证,以验证FPGA软件的功能和性能

4.2 FPGA软件维护

维护阶段是确保FPGA软件持续满足用户需求的过程。关键活动包括:

定期进行软件性能监测和问题排查,以确保软件的稳定性和可靠性

及时修复软件中发现的错误和漏洞,进行版本管理和发布控制

监测用户反馈和需求变化,进行系统优化和改进

5. FPGA软件自动化测试平台的设计与实现

FPGA软件自动化测试平台在当前的FPGA开发中具有重要作用。它解决了FPGA测试过程中的问题,提高了测试质量和效率。详细步骤和说明:

5.1 硬件环境的动态FPGA测试平台架构设计

硬件环境的动态FPGA测试平台架构设计可规范、标准化和自动化FPGA测试工具的测试流程,从而提高测试的质量和效率[1]。关键活动包括:

设计测试平台的总体架构和组成模块

开发测试平台的自动化控制和测试脚本

进行测试平台的验证和性能评估

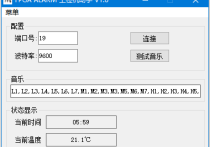

5.2 基于Testbench的FPGA实物自动化测试环境设计

基于Testbench的FPGA实物自动化测试环境设计利用真实的FPGA和软件半实物仿真测试环境进行自动化测试和全面性测试[2]。关键活动包括:

搭建FPGA实物仿真测试环境

开发自动化测试脚本和工具

执行全面性测试和性能评估

参考文献:

[0]: "载人航天工程FPGA软件研制技术培训-培训1-FPGA软件需求分析(公开)" 中国航天科技集团有限公司第704研究所,曹新恩

[1]: "一种fpga测试工具一体化测试管理平台" 链接

[2]: "基于Testbench的FPGA实物自动化测试环境设计" 链接