VHDL中的结构体 Architecture (二)

此点必须额外注意,当你初始化值时,可以用:=,但是给信号赋值就是<=

信号和变量的区别主要是信号的值为进程或者子程序最后的赋值结果,变量的赋值是立即生效的。

例如:

architecture behaviorl of count is signal a,b,c,d: std_logic_vector(3 downto 0); begin process(a,b,c,d) begin d<=a; x<=b+d; d<=c; y<=b+d; end process; end behaviorl;

运行后的结果为:x=b+c;

y=b+c;

而倘若D为变量类型:

architecture behaviorl of count is signal a,b,c: std_logic_vector(3 downto 0); begin process(a,b,c) variable d:std_logic_vector(3 downto 0); begin d<=a; x<=b+d; d<=c; y<=b+d; end process; end behaviorl;

运行后的结果为:x=b+a;

y=b+c;

观察可以发现,当abcd均为信号类型时,x和y的值,也就是b+d是取的b和d最后一次被赋值的结果,即b+d

而当d为变量类型后,x<=b+d的结果就是立即赋值的x<=b+a,倘若在后面b也发送了变化,则b也需要变为对应的值,但是此处d就是a不变的

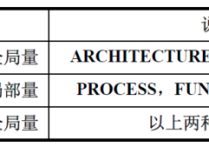

architecture中第二个部分就是处理部分,可以是进程 block 信号赋值 子程序调用 元件例化,上面说过,architecture中的语句和模块是并行进行的,但是process和subprogram内部是顺序的

例如:

architecture abc of bcd is signal time1:std_logic_bit; begin process(time1) time1<='1' after 10ns; time1<='0' after 20ns; end process; end abc;

在10ns之后,time1被赋值为1,再等待20ns之后,time1被赋值为0.